編程設計采用VHDL語言。VHDL主要用于描述數(shù)字系統(tǒng)的結構、行為�����、功能和接口�。除了含有許多硬件特征的語句外���,VHDL的語言形式和描述風格與句法十分類似于一般的計算機高級語言����。一個完整的VHDL語言程序通常含有5個部分:實體(Entity)�、結構體(ArcbAtecture)���、配置(Configuration)����、程序包(Package)和庫(Library)���。

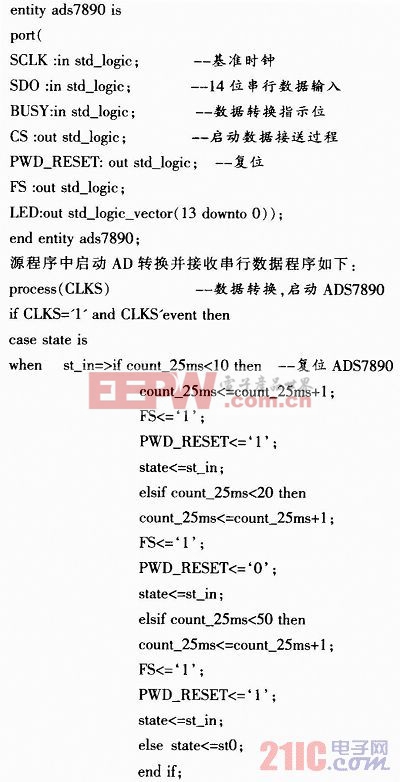

源程序中的結構體定義如下���。注意ADS7890的輸入對應的是EP2C35F672C6的輸出。

fpga相關文章:fpga是什么

評論